KL-300

259675₽

Цены на сайте указаны с НДС.

Под заказ возможна оперативная поставка любого количества.

- Хотите дешевле?

- Доставка по всему миру. Подробнее

Особенности Учебный стенд для изучения цифровых схем KL-300

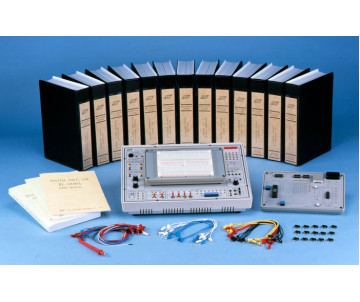

Учебный стенд для изучения и экспериментов с цифровыми электрическими схемами. Основной модуль содержит оборудование, необходимое для проведения экспериментов: источник электропитания, генератор сигнала, переключатели и индикаторы. 13 сменных экспериментальных модулей позволяют выполнять большое количество различных экспериментов по цифровой схемотехнике.

В состав стенда входит универсальная макетная плата (1680 точек подключения) для проектирования и исследования собственных электрических цепей.

Все модули оснащены 8-битными DIP микропереключателями для имитации неполадок в цепи.

Стенд позволяет работать с цифровыми схемами на основе ТТЛ, КМОП, n-канальной МОП, p-канальной МОП и ЭСЛ технологий

В целях безопасности все блоки питания снабжены защитой от перегрузки по выходу

Для удобства хранения и транспортировки все модули размещаются в отдельных пластиковых футлярах

Состав:

KL-31001 Основной модуль

KL-33001~KL-33013 Cменные модули

KL-38002 Набор соединительных проводов и принадлежностей

Руководство по экспериментам

РЕКОМЕНДУЕМОЕ ДОПОЛНИТЕЛЬНОЕ ОБОРУДОВАНИЕ (НЕ ВХОДИТ В КОМПЛЕКТ СТЕНДА):

Осциллограф, мультиметр

ПЕРЕЧЕНЬ ЭКСПЕРИМЕНТОВ

1 Эксперименты с основными логическими элементами

1-1 Введение в логические элементы и переключатели

1-2 Схемы логических элементов

a. Диодные логические схемы

b. Резисторно-транзисторные логические схемы (РТЛ)

c. Диодно-транзисторные логические схемы (ДТЛ)

d. Транзисторно-транзисторные логические схемы (ТТЛ)

e. Схемы на комплементарных металоксидных полупроводниках (КМОП)

1-3 Измерение пороговых уровней напряжения

a. Измерение пороговых уровней напряжений в схемах ТТЛ

b. Измерение пороговых уровней напряжений в схемах КМОП

1-4 Измерение напряжения/тока

a. Измерение входных/выходных напряжений и токов в схеме ТТЛ

b. Измерение напряжений и токов в схемах КМОП

1-5 Измерение временной задержки в основных логических элементах

a. Измерение временной задержки в схемах ТТЛ

b. Измерение временной задержки в схемах КМОП

1-6 Измерение характеристик основных логических элементов

a. Измерение характеристик элемента И

b. Измерение характеристик логического элемента ИЛИ

c. Измерение характеристик логического элемента НЕ

d. Измерение характеристик логического элемента И-НЕ

e. Измерение характеристик логического элемента ИЛИ-НЕ

f. Измерение характеристик логического элемента Искл. ИЛИ

1-7 Схемы преобразователей уровня для логических элементов

a. Схема преобразования уровней между элементами ТТЛ и КМОП

b. Схема преобразования уровней между элементами КМОП и ТТЛ

2 Эксперименты с комбинационными логическими схемами

2-1 Схема элемента ИЛИ-НЕ

2-2 Схема элемента И-НЕ

a. Построение элемента Искл. ИЛИ на основе элементов И-НЕ

b. Построение элемента Искл. ИЛИ на основе простых логических элементов

2-4 Схема элемента И-ИЛИ-НЕ

2-5 Схема компаратора

a. Построение компаратора на основе простых логических элементов

b. Построение компаратора на интегральной микросхеме семейства ТТЛ

2-6 Схема триггера Шмита

2-7 Схема элемента с открытым коллектором

a. Схема с высокими уровнями напряжений/токов

b. Построение элемента И на основе элемента с открытым коллектором

2-8 Схема элемента с третьим состоянием

a. Построение таблицы истинности

b. Построение элемента И на основе элемента с третьим состоянием

c. Схема двунаправленного передатчика

2-9 Схема полусумматора и полного сумматора

a. Построение схемы полусумматора на основе простых логических элементов

b. Схема полного сумматора на интегральной микросхеме

c. Схема высокоскоростного сумматора с генератором бита переноса

d. Схема двоично-десятичного сумматора

2-10 Схема полу- и полного вычитающего устройства

a. Построение схемы вычитающего устройства на основе простых логических элементов

b. Схема полного сумматора и инвертора

2-11 Схема арифметико-логического устройства

2-12 Схема формирования бита четности

a. Построение генератора бита четности на основе элементов Искл. ИЛИ

b. Генератор с битом четности на основе интегральной микросхемы

2-13 Схема шифратора

a. Построение схемы шифратора 4-в-2 на основе простых логических элементов

b. Построение схемы шифратора 9-в-4 на основе ИС семейства ТТЛ

2-14 Схема дешифратора

a. Построение схемы дешифратора 2-в-4 на основе простых логических элементов

b. Построение схемы дешифратора 4-в-10 на основе ИС семейства ТТЛ

2-15 Схема мультиплексора

a. Построение схемы мультиплексора 2-в-1

b. Использование мультиплексоров для построения функций

c. Построение схемы мультиплексора 8-в-1 на основе ИС семейства ТТЛ

2-16 Схема демультиплексора

a. Построение 2-выходного демультиплексора на основе простых логических элементов

b. Построение 8-выходного демультиплексора на основе ИС семейства КМОП

2-17 Схема аналогового мультиплексора/демультиплексора с цифровым управлением

a. Характеристики аналоговых ключей

b. Построение двунаправленного передатчика на основе ИС аналоговых ключей семейства КМОП

3 Эксперименты с генераторами

3-1 Построение генератора на основе простых логических элементов

3-2 Построение генератора на триггере Шмита

3-3 Построение генератора, управляемого напряжением (ГУН)

3-4 Схемы генераторов на ИС серии 555

a. Схема генератора 555

b. Схема ГУН

3-5 Схемы моностабильного мультивибратора

a. Схемы низкочастотного моностабильного мультивибратора

b. Схемы высокочастотного моностабильного мультивибратора

c. Построение моностабильного мультивибратора на микросхеме серии 555

d. Построение схемы без перезапуска на основе ИС семейства ТТЛ

e. Построение схемы с перезапуском на основе ИС семейства ТТЛ

f. Построение генератора с изменяемой длительностью цикла (ШИМ) на основе моностабильного мультивибратора

4 Эксперименты с последовательными логическими схемами

4-1 Схемы триггеров

a. Построение R-S триггера на основе простых логических элементов

b. Построение D триггера на основе R-S триггера

c. Построение J-K триггера на основе D триггера

d. Построение J-K триггера на основе R-S триггера

e. Построение сдвигового регистра на основе D триггеров

f. Регистр с предварительной установкой направления сдвига влево/вправо

g. Построение схемы подавления шумов на R-S триггере

4-2 Схемы J-K триггеров

a. Асинхронный двоичный суммирующий счетчик

b. Асинхронный десятичный суммирующий счетчик

c. Асинхронный суммирующий счетчик с делением на N

d. Асинхронный двоичный вычитающий счетчик

e. Синхронный двоичный суммирующий счетчик

f. Синхронный двоичный реверсивный счетчик

g. Двоичный реверсивный счетчик с установкой направления счета

h. Десятичный реверсивный счетчик с установкой направления счета

i. Кольцевой счетчик

j. Счетчик Джонсона

5 Эксперименты со схемами памяти

5-1 Построение постоянного запоминающего устройства (ПЗУ) на диодах

5-2 Построение оперативного запоминающего устройства (ОЗУ) на D триггерах

5-3 Схема 64-разрядной ОЗУ

5-4 Схема стираемого программируемого постоянного запоминающего устройства (EPROM)

5-5 Схема электронной EPROM (EEPROM)

5-6 Построение счетчика с динамическим сканированием с помощью однокристального микропроцессора

6 Эксперименты со схемами преобразователей уровней

6-1 Схемы цифро/аналоговых преобразователей (ЦАП)…

a. Схема однополярного ЦАП

b. Схема двуполярного ЦАП

6-2 Схемы аналогово/цифровых преобразователей (АЦП)

a. Схема 8-разрядного преобразователя

b. Схема 3 ½ разрядного преобразователя

7 Примеры построения схем с помощью универсальной макетной платы

7-1 4-канальный сенсорный селекторный переключатель

7-2 Электронный орган

7-3 Логический индикатор

7-4 Моностабильный кодовый замок

7-6 Электронный секундомер

7-7 Метроном с мигающими светодиодами

7-8 Счетчик входов/выходов

7-9 Многонаправленный ключ

7-10 Электронные часы

7-11 Счетчик частоты

7-12 Телефонный звонок

7-13 Светофор

7-14 Схема управления программируемым шаговым двигателем

В состав стенда входит универсальная макетная плата (1680 точек подключения) для проектирования и исследования собственных электрических цепей.

Все модули оснащены 8-битными DIP микропереключателями для имитации неполадок в цепи.

Стенд позволяет работать с цифровыми схемами на основе ТТЛ, КМОП, n-канальной МОП, p-канальной МОП и ЭСЛ технологий

В целях безопасности все блоки питания снабжены защитой от перегрузки по выходу

Для удобства хранения и транспортировки все модули размещаются в отдельных пластиковых футлярах

Состав:

KL-31001 Основной модуль

KL-33001~KL-33013 Cменные модули

KL-38002 Набор соединительных проводов и принадлежностей

Руководство по экспериментам

РЕКОМЕНДУЕМОЕ ДОПОЛНИТЕЛЬНОЕ ОБОРУДОВАНИЕ (НЕ ВХОДИТ В КОМПЛЕКТ СТЕНДА):

Осциллограф, мультиметр

ПЕРЕЧЕНЬ ЭКСПЕРИМЕНТОВ

1 Эксперименты с основными логическими элементами

1-1 Введение в логические элементы и переключатели

1-2 Схемы логических элементов

a. Диодные логические схемы

b. Резисторно-транзисторные логические схемы (РТЛ)

c. Диодно-транзисторные логические схемы (ДТЛ)

d. Транзисторно-транзисторные логические схемы (ТТЛ)

e. Схемы на комплементарных металоксидных полупроводниках (КМОП)

1-3 Измерение пороговых уровней напряжения

a. Измерение пороговых уровней напряжений в схемах ТТЛ

b. Измерение пороговых уровней напряжений в схемах КМОП

1-4 Измерение напряжения/тока

a. Измерение входных/выходных напряжений и токов в схеме ТТЛ

b. Измерение напряжений и токов в схемах КМОП

1-5 Измерение временной задержки в основных логических элементах

a. Измерение временной задержки в схемах ТТЛ

b. Измерение временной задержки в схемах КМОП

1-6 Измерение характеристик основных логических элементов

a. Измерение характеристик элемента И

b. Измерение характеристик логического элемента ИЛИ

c. Измерение характеристик логического элемента НЕ

d. Измерение характеристик логического элемента И-НЕ

e. Измерение характеристик логического элемента ИЛИ-НЕ

f. Измерение характеристик логического элемента Искл. ИЛИ

1-7 Схемы преобразователей уровня для логических элементов

a. Схема преобразования уровней между элементами ТТЛ и КМОП

b. Схема преобразования уровней между элементами КМОП и ТТЛ

2 Эксперименты с комбинационными логическими схемами

2-1 Схема элемента ИЛИ-НЕ

2-2 Схема элемента И-НЕ

a. Построение элемента Искл. ИЛИ на основе элементов И-НЕ

b. Построение элемента Искл. ИЛИ на основе простых логических элементов

2-4 Схема элемента И-ИЛИ-НЕ

2-5 Схема компаратора

a. Построение компаратора на основе простых логических элементов

b. Построение компаратора на интегральной микросхеме семейства ТТЛ

2-6 Схема триггера Шмита

2-7 Схема элемента с открытым коллектором

a. Схема с высокими уровнями напряжений/токов

b. Построение элемента И на основе элемента с открытым коллектором

2-8 Схема элемента с третьим состоянием

a. Построение таблицы истинности

b. Построение элемента И на основе элемента с третьим состоянием

c. Схема двунаправленного передатчика

2-9 Схема полусумматора и полного сумматора

a. Построение схемы полусумматора на основе простых логических элементов

b. Схема полного сумматора на интегральной микросхеме

c. Схема высокоскоростного сумматора с генератором бита переноса

d. Схема двоично-десятичного сумматора

2-10 Схема полу- и полного вычитающего устройства

a. Построение схемы вычитающего устройства на основе простых логических элементов

b. Схема полного сумматора и инвертора

2-11 Схема арифметико-логического устройства

2-12 Схема формирования бита четности

a. Построение генератора бита четности на основе элементов Искл. ИЛИ

b. Генератор с битом четности на основе интегральной микросхемы

2-13 Схема шифратора

a. Построение схемы шифратора 4-в-2 на основе простых логических элементов

b. Построение схемы шифратора 9-в-4 на основе ИС семейства ТТЛ

2-14 Схема дешифратора

a. Построение схемы дешифратора 2-в-4 на основе простых логических элементов

b. Построение схемы дешифратора 4-в-10 на основе ИС семейства ТТЛ

2-15 Схема мультиплексора

a. Построение схемы мультиплексора 2-в-1

b. Использование мультиплексоров для построения функций

c. Построение схемы мультиплексора 8-в-1 на основе ИС семейства ТТЛ

2-16 Схема демультиплексора

a. Построение 2-выходного демультиплексора на основе простых логических элементов

b. Построение 8-выходного демультиплексора на основе ИС семейства КМОП

2-17 Схема аналогового мультиплексора/демультиплексора с цифровым управлением

a. Характеристики аналоговых ключей

b. Построение двунаправленного передатчика на основе ИС аналоговых ключей семейства КМОП

3 Эксперименты с генераторами

3-1 Построение генератора на основе простых логических элементов

3-2 Построение генератора на триггере Шмита

3-3 Построение генератора, управляемого напряжением (ГУН)

3-4 Схемы генераторов на ИС серии 555

a. Схема генератора 555

b. Схема ГУН

3-5 Схемы моностабильного мультивибратора

a. Схемы низкочастотного моностабильного мультивибратора

b. Схемы высокочастотного моностабильного мультивибратора

c. Построение моностабильного мультивибратора на микросхеме серии 555

d. Построение схемы без перезапуска на основе ИС семейства ТТЛ

e. Построение схемы с перезапуском на основе ИС семейства ТТЛ

f. Построение генератора с изменяемой длительностью цикла (ШИМ) на основе моностабильного мультивибратора

4 Эксперименты с последовательными логическими схемами

4-1 Схемы триггеров

a. Построение R-S триггера на основе простых логических элементов

b. Построение D триггера на основе R-S триггера

c. Построение J-K триггера на основе D триггера

d. Построение J-K триггера на основе R-S триггера

e. Построение сдвигового регистра на основе D триггеров

f. Регистр с предварительной установкой направления сдвига влево/вправо

g. Построение схемы подавления шумов на R-S триггере

4-2 Схемы J-K триггеров

a. Асинхронный двоичный суммирующий счетчик

b. Асинхронный десятичный суммирующий счетчик

c. Асинхронный суммирующий счетчик с делением на N

d. Асинхронный двоичный вычитающий счетчик

e. Синхронный двоичный суммирующий счетчик

f. Синхронный двоичный реверсивный счетчик

g. Двоичный реверсивный счетчик с установкой направления счета

h. Десятичный реверсивный счетчик с установкой направления счета

i. Кольцевой счетчик

j. Счетчик Джонсона

5 Эксперименты со схемами памяти

5-1 Построение постоянного запоминающего устройства (ПЗУ) на диодах

5-2 Построение оперативного запоминающего устройства (ОЗУ) на D триггерах

5-3 Схема 64-разрядной ОЗУ

5-4 Схема стираемого программируемого постоянного запоминающего устройства (EPROM)

5-5 Схема электронной EPROM (EEPROM)

5-6 Построение счетчика с динамическим сканированием с помощью однокристального микропроцессора

6 Эксперименты со схемами преобразователей уровней

6-1 Схемы цифро/аналоговых преобразователей (ЦАП)…

a. Схема однополярного ЦАП

b. Схема двуполярного ЦАП

6-2 Схемы аналогово/цифровых преобразователей (АЦП)

a. Схема 8-разрядного преобразователя

b. Схема 3 ½ разрядного преобразователя

7 Примеры построения схем с помощью универсальной макетной платы

7-1 4-канальный сенсорный селекторный переключатель

7-2 Электронный орган

7-3 Логический индикатор

7-4 Моностабильный кодовый замок

7-6 Электронный секундомер

7-7 Метроном с мигающими светодиодами

7-8 Счетчик входов/выходов

7-9 Многонаправленный ключ

7-10 Электронные часы

7-11 Счетчик частоты

7-12 Телефонный звонок

7-13 Светофор

7-14 Схема управления программируемым шаговым двигателем

Комплектация Учебный стенд для изучения цифровых схем KL-300

| Главный блок KL-31001 для присоединения модулей | 1 шт. |

| Модуль KL- 33001 для экспериментов с основными логическими схемами | 1 шт. |

| Модуль KL- 33002 для экспериментов со схемами комбинационной логики | 1 шт. |

| Модуль KL- 33003 с учебными схемами вентилей с тремя состояниями | 1 шт. |

| Модуль KL- 33004 с учебными схемами полусумматора и полного сумматора | 1 шт. |

| Модуль KL- 33005 с учебными схемами шифраторов и дешифраторов- | 1 шт. |

| Модуль KL-33006 с учебными схемами мультиплексоров- | 1 шт. |

| KL- 33007 для экспериментов со схемой генератора тактовых импульсов | 1 шт. |

| Модуль KL- 33008 для экспериментов со схемами последовательной логики | 1 шт. |

| Модуль KL- 33009 со учебными схемами JK - триггеров | 1 шт. |

| Модуль KL- 33010 для проведения экспериментов с ОЗУ | 1 шт. |

| Модуль KL- 33011 с учебной схемой программируемой постоянной памяти | 1 шт. |

| Модуль KL- 33012 для экспериментов со схемами преобразователей | 1 шт. |

| Модуль KL- 33013 с учебной схемой цифрового-аналогового преобразователя | 1 шт. |

| KL-300 Руководство по проведению экспериментов на английском языке | 1 шт. |

| KL-31001 Руководство пользователя на английском языке | 1 шт. |

| KL-38002: Соединительные провода и разъемы | 1 комплект |